# FUTUR-IC: Research Towards A Sustainable Microchip Industry - Manufacturing and Operation

Anu Agarwal Lionel C. Kimerling Randolph Kirchain Elsa Olivetti Samuel Serna anu@mit.edu lckim@mit.edu kirchain@mit.edu elsao@mit.edu ssernaotalvaro@bridgew.edu

**Overview**

The balance between human existence and microchip benefits is being severely challenged by a relentless and unsustainable appetite for electronics consumption. For the first time in more than 40 years, semiconductor microchip industry confronted with limits to transistor size, to its environmental footprint, and to its workforce pipeline readiness. With the National Science Convergence Foundation Accelerator program, we have established a global microchip sustainability project FUTUR-IC, which creates self-consistent 3D technology, ecology, and workforce research solutions to sustain the continued progress of the semiconductor manufacturing and the information systems industry. FUTUR-IC will enable companies to make multidecisions dimensional based the on consequences for people, planet, and profits.

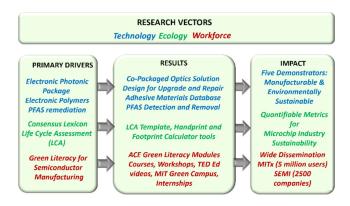

Figure 1. Holistic roadmap to innovate sustainably along the three critical dimensions of technology, ecology, and workforce, through consensus across the microchip supply chain.

## **Description**

Frontier constraints in the microchip industry are:

1) <u>Technology/Profits</u>: Enhanced microchip functionality for next generation applications such as AI, 6G, LiDAR etc. can no longer depend solely on shrinking the dimensions of a transistor;

2) <u>Ecology/Planet</u>: Net Zero environmental impact for a product life cycle is critical to life on earth; 3) <u>Workforce/People</u>: Leadership from a new green-literate STEM workforce is required. Concurrently engineered solutions are expected to build a common learning curve to power the next 40 years of progress for the semiconductor industry.

FUTUR-IC will: 1) Benefit consumers: Enhance life while targeting Net Zero environmental impact by 2050; 2) Foster future innovators and enhance full-spectrum workforce training: Extend green literacy in microchip technologies to recruit and retain from K-Gray; 3) Increase DEIA: Support diversity in leadership,

gender, ethnicity, and cultural backgrounds, to ensure that research is informed by a broad range of perspectives to shape future technology trajectories; and 4) Transform the global microchip supply chain: Provide coherent technology evolution within the constraints of the environmental and social impacts of materials, processes, and designs.

Microchip manufacturing and systems can be traced to about 500 Megatonnes of CO2-eq lifetime emissions in 2021. Mega Data Centers consuming tens of Megawatts of power and growing at 25-30% per year driven by video demand, will require 10% of the world electricity generation by 2030. Regulatory solutions threaten to disrupt the economics of an efficient global supply chain. Technology solutions require synchronized innovation along the supply chain from materials suppliers to system integrators to end users. FUTUR-IC supports continued scaling of system performance while targeting Net Zero environmental impact by 2050 for the global community.

Semiconductor hardware, software and system architectures are undergoing simultaneous technology transitions today that present both opportunities and uncertainties. The information systems that drive Data Center workflows and ubiquitous sensing installations for the Internet of Things (IoT) aim to do the impossible: scale down costs, energy consumption, and latency to nearly zero, while simultaneously amplifying bandwidth and connectivity to seemingly infinite environmental constraints. levels, within Solutions defined by concurrent TEW constraints will build converged pathways on which to base decades of progress. The time to surmount these roadblocks for the microchip industry is *now*!

#### **Differentiators**

FUTUR-IC is a member-led association of thought leaders from industry, academia, and government, contributing via joint research projects to innovation in sustainable microchip technology development. Engineers, scientists, executives, and policy makers work together to assess and remedy common risks presented by technology change, ecology boundaries, and workforce competency. This unique Alliance creates consensus for investments with its 3D-TEW research model. FUTUR-IC accelerates convergence of materials science with life-cycle analysis to drive materials and process design towards sustainable processes and products.

#### Roadmap

Technology: FUTUR-IC has adopted electronic-photonic package integration as its hardware driver. It has targeted scaling chip package Input-Output (I/O) to > 1 Petabit/second within a Net Zero ecology envelope. Investment examples are: 1) PFAS-free materials and process flows to meet package scaling requirements; 2) adhesive materials database for low temperature assembly; and 3) demonstration of new chip package architectures that mitigate end-of-life waste with capability for repair and upgrade under a new Design for Upgrade, Repair, Reduce, Reuse, Recycle (DfUR<sup>4</sup>) initiative.

Ecology: FUTUR-IC will 1) create data analytics for environmental and social impacts of microchip product lifecycles; 2) develop a consensus set of figures of merit; 3) develop the tools and processes for timely Life Cycle

Assessment (LCA); 4) provide data and analysis for a guidance roadmap; and 5) provide tools for decreasing *footprint burdens and increasing handprint remediations*. (The handprint is an innovative and holistic approach to facilitate the measurement, evaluation, and communication of the ecological, economic, and social sustainability impacts of products).

Workforce: **FUTUR-IC** provides multidimensional TEW awareness that is transformed into solutions by its new educational curricula and content. Examples are: 1) SEMI (the microchip supply chain consortium) Green Literacy programs, 2) summer schools and boot camps, 3) university courses, 4) Problem Based Learning (PBL) for community colleges, 5) TED-Ed videos and Virtual Reality (VR) sustainability games for K-to-Gray learners, 6) two MIT green campus demonstrator sites for e-waste mitigation and green manufacturing materials and processes, 7) full spectrum internships for high school and community college students, and 8) annual workforce needs reports for each participating community.

## **Partnerships**

Figure 2. Current FUTUR-IC Partners

FUTUR-IC's partners have developed programs across all three TEW vectors. Examples are <u>Technology</u>: **iNEMI** (industry association for joint development projects) for adhesive package materials; <u>Ecology</u>: tools and processes for LCA and handprinting throughout the **microchip supply chain**; <u>Workforce</u>: **SEMI** sustainability literacy for executives and incumbent workers.

Figure 3. MIT Sustainability ecosystem – a testbed

MIT has a vibrant sustainability community with whom FUTUR-IC will collaborate, to generate ideas for new methods towards chip sustainability. MIT will serve as a testbed for "green research" and "green literacy" microchip educational programs, results of which will be disseminated to undergraduate and graduate students through courses, summer academies, bootcamps, and labs. Sustainability workshops will also be conducted for nearby community college students.

# **Intellectual Property**

FUTUR-IC has filed three patents for assembly and architecture for advanced packaging. Continued IP development is governed by three agreements: 1) shared rights under MIT's Industrial Consortium; 2) exclusive rights under negotiated research agreements; and 3) Joint Development Project rights under standard iNEMI protocols.

# The Package Scaling Era

The Chip Scaling Era has ended, and the Package/System Scaling Era is now in full implementation with **no long-term technology roadmap**. To maintain performance scaling: i) incremental technology change is insufficient, and ii) supply chain sustainability in terms of workforce quality, materials criticality, and manufacturing effluent has no inherent scaling vector. Economic risk has never been so large, and rarely been so dependent on a particular technology evolution.

This transformation to chip/package scaling is not a task that any one sector can tackle in isolation; it requires a robust global alliance that unites academia, industry, government, and community. FUTUR-IC offers such collective research projects and partnerships to pave the way for innovative solutions, ensuring a resilient and prosperous technological future.